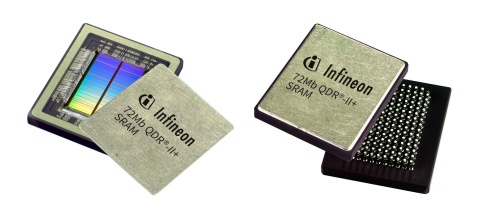

物料参数

| Architecture: | QDR-II+ |

| Bank Switching: | N |

| ECC: | N |

| Family: | QDR-II+ |

| Frequency: | 250.0MHz |

| Lead Ball Finish: | Sn/Pb |

| On-Die Termination: | N |

| Operating Temperature: | None°C |

| Organization (X x Y): | 2Mb x 36 |

| Peak Reflow Temp: | 260.0°C |

| Qualification: | Military |

| Read Latency (Cycles): | 2.0 |

| Data Width: | x 18 |

| Burst Length(Words): | 2 |

| Operating Voltage: | NoneV |

| Interfaces: | Parallel |

| Density: | 73728.0kBit |

| Density: | 72.0MBit |

无库存